#### Notes on ADC Setup

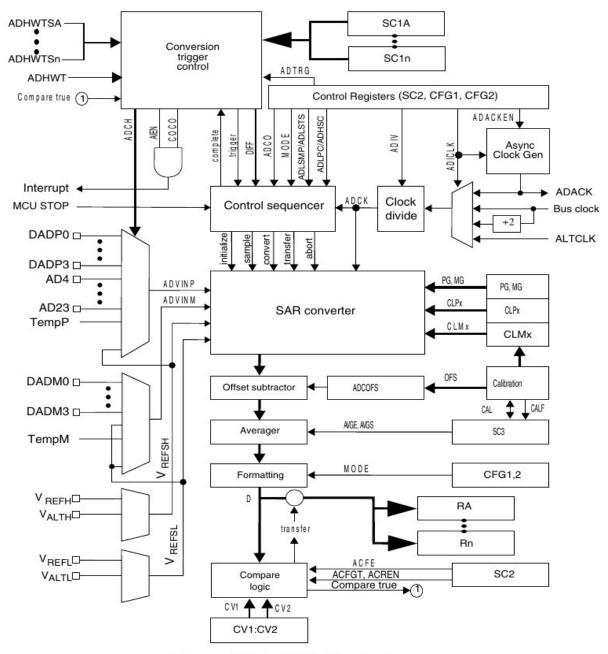

As can be seen in figure 28-1 below the ADC subsystem is somewhat complex. However, not all of its capabilities are needed for any particular project. This document summarizes configuration steps needed to start conversions from a hardware timer signal, sample one channel, possibly sample that one channel multiple times to find an average, and then generate an interrupt signaling that conversion is complete and new data is ready to be read from the ADC.

For reference, a block diagram of the ADC from page 459

Figure 28-1. ADC block diagram

Note: the clock to the ADC subsystem must be turned on before attempting to write to the various registers to configure the ADC.

Selecting ADC input channels.

There is one A/D converter with an analog switch ahead of it that allows selecting the analog source to be used by the converter. There are differential and a single-ended input modes. A differential mode requires two pins on the MCU, one to supply the positive and the other the negative input with the converter measuring the difference voltage between them. There are four possible pairs of differential input pins to select from (not all may be available on a particular version of the MCU chip). Single ended inputs require a single pin on the MCU and the measurement is referenced to Vssa, i.e. the analog ground pin. There are up to 15 pins from which to select the single ended analog signal plus several internal voltages.

Highlighted with red arrows or circles are parameters that should work for the class project.

| ADC Channel<br>(SC1n[ADCH]) | Channel | Input signal<br>(SC1n[DIFF]= 1) | Input signal<br>(SC1n[DIFF]= 0) |

|-----------------------------|---------|---------------------------------|---------------------------------|

| 00000                       | DAD0    | ADC0_DP0 and ADC0_DM0           | ADC0_DP0/ADC0_SE0               |

| 00001                       | DAD1    | ADC0_DP1 and ADC0_DM1           | ADC0_DP1/ADC0_SE1               |

| 00010                       | DAD2    | ADC0_DP2 and ADC0_DM2           | ADC0_DP2/ADC0_SE2               |

| 00011                       | DAD3    | ADC0_DP3 and ADC0_DM3           | ADC0_DP3/ADC0_SE3               |

| 00100 <sup>1</sup>          | AD4a    | Reserved                        | ADC0_DM0/ADC0_SE4a              |

| 00101 <sup>1</sup>          | AD5a    | Reserved                        | ADC0_DM1/ADC0_SE5a              |

| 00110 <sup>1</sup>          | AD6a    | Reserved                        | ADC0_DM2/ADC0_SE6a              |

| 00111 <sup>1</sup>          | AD7a    | Reserved                        | ADC0_DM3/ADC0_SE7a              |

| 00100 <sup>1</sup>          | AD4b    | Reserved                        | ADC0_SE4b                       |

| 00101 <sup>1</sup>          | AD5b    | Reserved                        | ADC0_SE5b                       |

| 00110 <sup>1</sup>          | AD6b    | Reserved                        | ADC0_SE6b                       |

| 00111 <sup>1</sup>          | AD7b    | Reserved                        | ADC0_SE7b                       |

| 01000                       | AD8     | Reserved                        | ADC0_SE8                        |

| 01001                       | AD9     | Reserved                        | ADC0_SE9                        |

| 01010                       | AD10    | Reserved                        | Reserved                        |

### 3.7.1.3.1 ADC0 Channel Assignment

Table continues on the next page...

From pages 79 - 80

(continue next page)

| ADC Channel<br>(SC1n[ADCH]) | Channel | Input signal<br>(SC1n[DIFF]= 1) | Input signal<br>(SC1n[DIFF]= 0)  |

|-----------------------------|---------|---------------------------------|----------------------------------|

| 01011                       | AD11    | Reserved                        | ADC0_SE11                        |

| 01100                       | AD12    | Reserved                        | ADC0_SE12                        |

| 01101                       | AD13    | Reserved                        | ADC0_SE13                        |

| 01110                       | AD14    | Reserved                        | ADC0_SE14                        |

| 01111                       | AD15    | Reserved                        | ADC0_SE15                        |

| 10000                       | AD16    | Reserved                        | Reserved                         |

| 10001                       | AD17    | Reserved                        | Reserved                         |

| 10010                       | AD18    | Reserved                        | Reserved                         |

| 10011                       | AD19    | Reserved                        | Reserved                         |

| 10100                       | AD20    | Reserved                        | Reserved                         |

| 10101                       | AD21    | Reserved                        | Reserved                         |

| 10110                       | AD22    | Reserved                        | Reserved                         |

| 10111                       | AD23    | Reserved                        | 12-bit DAC0 Output/<br>ADC0_SE23 |

| 11000                       | AD24    | Reserved                        | Reserved                         |

| 11001                       | AD25    | Reserved                        | Reserved                         |

| 11010                       | AD26    | Temperature Sensor (Diff)       | Temperature Sensor (S.E)         |

| 11011                       | AD27    | Bandgap (Diff) <sup>2</sup>     | Bandgap (S.E) <sup>2</sup>       |

| 11100                       | AD28    | Reserved                        | Reserved                         |

| 11101                       | AD29    | -VREFH (Diff)                   | VREFH (S.E)                      |

| 11110                       | AD30    | Reserved                        | VREFL                            |

| 11111                       | AD31    | Module Disabled                 | Module Disabled                  |

1. ADCx\_CFG2[MUXSEL] bit selects between ADCx\_SEn channels a and b. Refer to MUXSEL description in ADC chapter for details.

This is the PMC bandgap 1V reference voltage. Prior to reading from this ADC channel, ensure that you enable the bandgap buffer by setting the PMC\_REGSC[BGBE] bit. Refer to the device data sheet for the bandgap voltage (V<sub>BG</sub>) specification.

#### ADC trigger sources

An A/D conversion can be initiated in several ways (pg 201).

#### SIM\_SOPT7 field descriptions

| Field               | Description                                                                                     |

|---------------------|-------------------------------------------------------------------------------------------------|

| 31–8                | This field is reserved.                                                                         |

| Reserved            | This read-only field is reserved and always has the value 0.                                    |

| 7                   | ADC0 alternate trigger enable                                                                   |

| ADC0ALT1RGEN        |                                                                                                 |

|                     | Enable alternative conversion triggers for ADC0.                                                |

|                     | 0 TPM1 channel 0 (A) and channel 1 (B) triggers selected for ADC0.                              |

| $ \longrightarrow $ | 1 Alternate trigger selected for ADC0.                                                          |

| 6–5                 | This field is reserved.                                                                         |

| Reserved            | This read-only field is reserved and always has the value 0.                                    |

| 4                   | ADC0 pretrigger select                                                                          |

| ADC0PRETRGSEL       |                                                                                                 |

|                     | Selects the ADC0 pre-trigger source when alternative triggers are enabled through ADC0ALTTRGEN. |

| $\rightarrow$       | 0 Pre-trigger A                                                                                 |

|                     | 1 Pre-trigger B                                                                                 |

| 3-0                 | ADC0 trigger select                                                                             |

| ADC01RGSEL          |                                                                                                 |

|                     | Selects the ADC0 trigger source when alternative triggers are functional in stop and VLPS modes |

|                     | 0000 External trigger pin input (EXTRG_IN)                                                      |

|                     | 0001 CMP0 output                                                                                |

|                     | 0010 Reserved                                                                                   |

|                     | 0011 Reserved                                                                                   |

| $\rightarrow$       | 0100 PIT trigger 0                                                                              |

|                     | 0101 PIT trigger 1                                                                              |

|                     | 0110 Reserved                                                                                   |

|                     | 0111 Reserved                                                                                   |

|                     | 1000 TPM0 overflow                                                                              |

|                     | 1001 TPM1 overflow                                                                              |

|                     | 1010 TPM2 overflow                                                                              |

|                     | 1011 Reserved                                                                                   |

|                     | 1100 RTC alarm                                                                                  |

|                     | 1101 RTC seconds                                                                                |

|                     | 1110 LPTMR0 trigger                                                                             |

|                     | 1111 Reserved                                                                                   |

Example statements to configure the SIM SOPT7 register

SIM->SOPT7 |= SIM\_SOPT7\_ADC0ALTTRGEN(1); SIM->SOPT7 |= SIM\_SOPT7\_ADC0PRETRGSEL(0); SIM->SOPT7 |= SIM\_SOPT7\_ADC0TRGSEL(9);

// selects TPM1 overflow

// PIT trigger 0 could be used

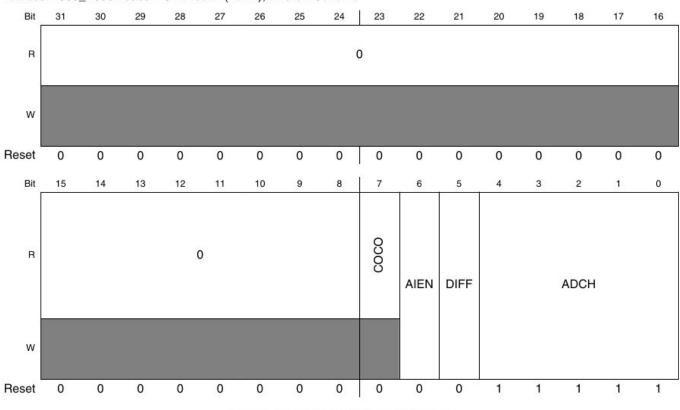

Address: 4003\_B000h base + 0h offset + (4d × i), where i=0d to 1d

#### ADCx\_SC1n field descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31–8<br>Reserved | This field is reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                  | This read-only field is reserved and always has the value 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 7<br>COCO        | Conversion Complete Flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                  | This is a read-only field that is set each time a conversion is completed when the compare function is disabled, or SC2[ACFE]=0 and the hardware average function is disabled, or SC3[AVGE]=0. When the compare function is enabled, or SC2[ACFE]=1, COCO is set upon completion of a conversion only if the compare result is true. When the hardware average function is enabled, or SC3[AVGE]=1, COCO is set upon completion of the selected number of conversions (determined by AVGS). COCO in SC1A is also set at the completion of a calibration sequence. COCO is cleared when the respective SC1n register is written or when the respective Rn register is read. |

|                  | 0 Conversion is not completed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                  | 1 Conversion is completed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6<br>AIEN        | Interrupt Enable<br>Enables conversion complete interrupts. When COCO becomes set while the respective AIEN is high, an                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                  | interrupt is asserted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                  | 0 Conversion complete interrupt is disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| $\rightarrow$    | 1 Conversion complete interrupt is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5<br>DIFF        | Differential Mode Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                  | Configures the ADC to operate in differential mode. When enabled, this mode automatically selects from the differential channels, and changes the conversion algorithm and the number of cycles to complete a conversion.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| $\rightarrow$    | 0 Single-ended conversions and input channels are selected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                  | 1 Differential conversions and input channels are selected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4–0   | Input channel select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADCH  | Selects one of the input channels. The input channel decode depends on the value of DIFF. DAD0-DA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|       | are associated with the input pin pairs DADPx and DADMx.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|       | <b>NOTE:</b> Some of the input channel options in the bitfield-setting descriptions might not be available for your device. For the actual ADC channel assignments for your device, see the Chip Configura details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|       | The successive approximation converter subsystem is turned off when the channel select bits are all set that is, ADCH = 11111. This feature allows explicit disabling of the ADC and isolation of the input channel from all sources. Terminating continuous conversions this way prevents an additional single conversion from being performed. It is not necessary to set ADCH to all 1s to place the ADC in a low-power state when continuous conversions are not enabled because the module automatically enters a low-power state when a conversion completes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|       | 00000 When DIFF=0, DADP0 is selected as input; when DIFF=1, DAD0 is selected as input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| -     | 00001 When DIFF=0, DADP1 is selected as input; when DIFF=1, DAD1 is selected as input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       | 00010 When DIFF=0, DADP2 is selected as input; when DIFF=1, DAD2 is selected as input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       | 00011 When DIFF=0, DADP3 is selected as input; when DIFF=1, DAD3 is selected as input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       | 00100 When DIFF=0, AD4 is selected as input; when DIFF=1, it is reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | 00101 When DIFF=0, AD5 is selected as input; when DIFF=1, it is reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | 00110 When DIFF=0, AD6 is selected as input; when DIFF=1, it is reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | 00111 When DIFF=0, AD7 is selected as input; when DIFF=1, it is reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | 01000 When DIFF=0, AD8 is selected as input; when DIFF=1, it is reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | 01001 When DIFF=0, AD9 is selected as input; when DIFF=1, it is reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | 01010 When DIFF=0, AD10 is selected as input; when DIFF=1, it is reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|       | 01011 When DIFF=0, AD11 is selected as input; when DIFF=1, it is reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Field | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       | 01100 When DIFF=0, AD12 is selected as input; when DIFF=1, it is reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       | 01101 When DIFF=0, AD13 is selected as input; when DIFF=1, it is reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|       | <ul> <li>When DIFF=0, AD13 is selected as input; when DIFF=1, it is reserved.</li> <li>When DIFF=0, AD14 is selected as input; when DIFF=1, it is reserved.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       | <ul> <li>01101 When DIFF=0, AD13 is selected as input; when DIFF=1, it is reserved.</li> <li>01110 When DIFF=0, AD14 is selected as input; when DIFF=1, it is reserved.</li> <li>01111 When DIFF=0, AD15 is selected as input; when DIFF=1, it is reserved.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       | <ul> <li>When DIFF=0, AD13 is selected as input; when DIFF=1, it is reserved.</li> <li>When DIFF=0, AD14 is selected as input; when DIFF=1, it is reserved.</li> <li>When DIFF=0, AD15 is selected as input; when DIFF=1, it is reserved.</li> <li>When DIFF=0, AD16 is selected as input; when DIFF=1, it is reserved.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|       | <ul> <li>01101 When DIFF=0, AD13 is selected as input; when DIFF=1, it is reserved.</li> <li>01110 When DIFF=0, AD14 is selected as input; when DIFF=1, it is reserved.</li> <li>01111 When DIFF=0, AD15 is selected as input; when DIFF=1, it is reserved.</li> <li>10000 When DIFF=0, AD16 is selected as input; when DIFF=1, it is reserved.</li> <li>10001 When DIFF=0, AD17 is selected as input; when DIFF=1, it is reserved.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|       | <ul> <li>01101 When DIFF=0, AD13 is selected as input; when DIFF=1, it is reserved.</li> <li>01110 When DIFF=0, AD14 is selected as input; when DIFF=1, it is reserved.</li> <li>01111 When DIFF=0, AD15 is selected as input; when DIFF=1, it is reserved.</li> <li>10000 When DIFF=0, AD16 is selected as input; when DIFF=1, it is reserved.</li> <li>10001 When DIFF=0, AD17 is selected as input; when DIFF=1, it is reserved.</li> <li>10010 When DIFF=0, AD18 is selected as input; when DIFF=1, it is reserved.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|       | <ul> <li>01101 When DIFF=0, AD13 is selected as input; when DIFF=1, it is reserved.</li> <li>01110 When DIFF=0, AD14 is selected as input; when DIFF=1, it is reserved.</li> <li>01111 When DIFF=0, AD15 is selected as input; when DIFF=1, it is reserved.</li> <li>10000 When DIFF=0, AD16 is selected as input; when DIFF=1, it is reserved.</li> <li>10001 When DIFF=0, AD17 is selected as input; when DIFF=1, it is reserved.</li> <li>10010 When DIFF=0, AD18 is selected as input; when DIFF=1, it is reserved.</li> <li>10010 When DIFF=0, AD18 is selected as input; when DIFF=1, it is reserved.</li> <li>10011 When DIFF=0, AD19 is selected as input; when DIFF=1, it is reserved.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|       | <ul> <li>01101 When DIFF=0, AD13 is selected as input; when DIFF=1, it is reserved.</li> <li>01110 When DIFF=0, AD14 is selected as input; when DIFF=1, it is reserved.</li> <li>01111 When DIFF=0, AD15 is selected as input; when DIFF=1, it is reserved.</li> <li>10000 When DIFF=0, AD16 is selected as input; when DIFF=1, it is reserved.</li> <li>10001 When DIFF=0, AD17 is selected as input; when DIFF=1, it is reserved.</li> <li>10010 When DIFF=0, AD18 is selected as input; when DIFF=1, it is reserved.</li> <li>10011 When DIFF=0, AD19 is selected as input; when DIFF=1, it is reserved.</li> <li>10011 When DIFF=0, AD19 is selected as input; when DIFF=1, it is reserved.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|       | <ul> <li>01101 When DIFF=0, AD13 is selected as input; when DIFF=1, it is reserved.</li> <li>01110 When DIFF=0, AD14 is selected as input; when DIFF=1, it is reserved.</li> <li>01111 When DIFF=0, AD15 is selected as input; when DIFF=1, it is reserved.</li> <li>10000 When DIFF=0, AD16 is selected as input; when DIFF=1, it is reserved.</li> <li>10001 When DIFF=0, AD17 is selected as input; when DIFF=1, it is reserved.</li> <li>10010 When DIFF=0, AD18 is selected as input; when DIFF=1, it is reserved.</li> <li>10011 When DIFF=0, AD19 is selected as input; when DIFF=1, it is reserved.</li> <li>10100 When DIFF=0, AD20 is selected as input; when DIFF=1, it is reserved.</li> <li>10101 When DIFF=0, AD21 is selected as input; when DIFF=1, it is reserved.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|       | <ul> <li>01101 When DIFF=0, AD13 is selected as input; when DIFF=1, it is reserved.</li> <li>01110 When DIFF=0, AD14 is selected as input; when DIFF=1, it is reserved.</li> <li>01111 When DIFF=0, AD15 is selected as input; when DIFF=1, it is reserved.</li> <li>10000 When DIFF=0, AD16 is selected as input; when DIFF=1, it is reserved.</li> <li>10001 When DIFF=0, AD17 is selected as input; when DIFF=1, it is reserved.</li> <li>10010 When DIFF=0, AD18 is selected as input; when DIFF=1, it is reserved.</li> <li>10011 When DIFF=0, AD18 is selected as input; when DIFF=1, it is reserved.</li> <li>10011 When DIFF=0, AD19 is selected as input; when DIFF=1, it is reserved.</li> <li>10100 When DIFF=0, AD20 is selected as input; when DIFF=1, it is reserved.</li> <li>10101 When DIFF=0, AD21 is selected as input; when DIFF=1, it is reserved.</li> <li>10110 When DIFF=0, AD21 is selected as input; when DIFF=1, it is reserved.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       | <ul> <li>01101 When DIFF=0, AD13 is selected as input; when DIFF=1, it is reserved.</li> <li>01110 When DIFF=0, AD14 is selected as input; when DIFF=1, it is reserved.</li> <li>01111 When DIFF=0, AD15 is selected as input; when DIFF=1, it is reserved.</li> <li>10000 When DIFF=0, AD16 is selected as input; when DIFF=1, it is reserved.</li> <li>10001 When DIFF=0, AD17 is selected as input; when DIFF=1, it is reserved.</li> <li>10010 When DIFF=0, AD18 is selected as input; when DIFF=1, it is reserved.</li> <li>10011 When DIFF=0, AD19 is selected as input; when DIFF=1, it is reserved.</li> <li>10011 When DIFF=0, AD20 is selected as input; when DIFF=1, it is reserved.</li> <li>10100 When DIFF=0, AD21 is selected as input; when DIFF=1, it is reserved.</li> <li>10111 When DIFF=0, AD21 is selected as input; when DIFF=1, it is reserved.</li> <li>10111 When DIFF=0, AD23 is selected as input; when DIFF=1, it is reserved.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       | <ul> <li>01101 When DIFF=0, AD13 is selected as input; when DIFF=1, it is reserved.</li> <li>01110 When DIFF=0, AD14 is selected as input; when DIFF=1, it is reserved.</li> <li>01111 When DIFF=0, AD15 is selected as input; when DIFF=1, it is reserved.</li> <li>10000 When DIFF=0, AD16 is selected as input; when DIFF=1, it is reserved.</li> <li>10001 When DIFF=0, AD17 is selected as input; when DIFF=1, it is reserved.</li> <li>10010 When DIFF=0, AD18 is selected as input; when DIFF=1, it is reserved.</li> <li>10011 When DIFF=0, AD19 is selected as input; when DIFF=1, it is reserved.</li> <li>10011 When DIFF=0, AD20 is selected as input; when DIFF=1, it is reserved.</li> <li>10101 When DIFF=0, AD21 is selected as input; when DIFF=1, it is reserved.</li> <li>10110 When DIFF=0, AD21 is selected as input; when DIFF=1, it is reserved.</li> <li>10110 When DIFF=0, AD21 is selected as input; when DIFF=1, it is reserved.</li> <li>10110 When DIFF=0, AD23 is selected as input; when DIFF=1, it is reserved.</li> <li>10111 When DIFF=0, AD23 is selected as input; when DIFF=1, it is reserved.</li> <li>10110 Reserved.</li> </ul>                                                                                                                                                                                                                                                                                                                                                   |

|       | <ul> <li>01101 When DIFF=0, AD13 is selected as input; when DIFF=1, it is reserved.</li> <li>01110 When DIFF=0, AD14 is selected as input; when DIFF=1, it is reserved.</li> <li>01111 When DIFF=0, AD15 is selected as input; when DIFF=1, it is reserved.</li> <li>10000 When DIFF=0, AD16 is selected as input; when DIFF=1, it is reserved.</li> <li>10001 When DIFF=0, AD17 is selected as input; when DIFF=1, it is reserved.</li> <li>10010 When DIFF=0, AD18 is selected as input; when DIFF=1, it is reserved.</li> <li>10011 When DIFF=0, AD18 is selected as input; when DIFF=1, it is reserved.</li> <li>10011 When DIFF=0, AD19 is selected as input; when DIFF=1, it is reserved.</li> <li>10100 When DIFF=0, AD20 is selected as input; when DIFF=1, it is reserved.</li> <li>10101 When DIFF=0, AD21 is selected as input; when DIFF=1, it is reserved.</li> <li>10110 When DIFF=0, AD21 is selected as input; when DIFF=1, it is reserved.</li> <li>10110 When DIFF=0, AD22 is selected as input; when DIFF=1, it is reserved.</li> <li>10111 When DIFF=0, AD23 is selected as input; when DIFF=1, it is reserved.</li> <li>10111 When DIFF=0, AD23 is selected as input; when DIFF=1, it is reserved.</li> <li>11000 Reserved.</li> <li>11001 Reserved.</li> <li>11001 When DIFF=0, Temp Sensor (single-ended) is selected as input; when DIFF=1, Temp Sensor</li> </ul>                                                                                                                                |

|       | <ul> <li>01101 When DIFF=0, AD13 is selected as input; when DIFF=1, it is reserved.</li> <li>01110 When DIFF=0, AD14 is selected as input; when DIFF=1, it is reserved.</li> <li>01111 When DIFF=0, AD15 is selected as input; when DIFF=1, it is reserved.</li> <li>10000 When DIFF=0, AD16 is selected as input; when DIFF=1, it is reserved.</li> <li>10001 When DIFF=0, AD17 is selected as input; when DIFF=1, it is reserved.</li> <li>10010 When DIFF=0, AD18 is selected as input; when DIFF=1, it is reserved.</li> <li>10010 When DIFF=0, AD19 is selected as input; when DIFF=1, it is reserved.</li> <li>10011 When DIFF=0, AD20 is selected as input; when DIFF=1, it is reserved.</li> <li>10100 When DIFF=0, AD21 is selected as input; when DIFF=1, it is reserved.</li> <li>10110 When DIFF=0, AD21 is selected as input; when DIFF=1, it is reserved.</li> <li>10110 When DIFF=0, AD22 is selected as input; when DIFF=1, it is reserved.</li> <li>10110 When DIFF=0, AD23 is selected as input; when DIFF=1, it is reserved.</li> <li>10111 When DIFF=0, AD23 is selected as input; when DIFF=1, it is reserved.</li> <li>11000 Reserved.</li> <li>11001 Reserved.</li> <li>11010 When DIFF=0, Temp Sensor (single-ended) is selected as input; when DIFF=1, Temp Sensor (differential) is selected as input.</li> <li>11011 When DIFF=0, Bandgap (single-ended) is selected as input; when DIFF=1, Bandgap (differential)</li> </ul>                                                                  |

|       | <ul> <li>01101 When DIFF=0, AD13 is selected as input; when DIFF=1, it is reserved.</li> <li>01110 When DIFF=0, AD14 is selected as input; when DIFF=1, it is reserved.</li> <li>01111 When DIFF=0, AD15 is selected as input; when DIFF=1, it is reserved.</li> <li>10000 When DIFF=0, AD16 is selected as input; when DIFF=1, it is reserved.</li> <li>10001 When DIFF=0, AD17 is selected as input; when DIFF=1, it is reserved.</li> <li>10010 When DIFF=0, AD18 is selected as input; when DIFF=1, it is reserved.</li> <li>10010 When DIFF=0, AD19 is selected as input; when DIFF=1, it is reserved.</li> <li>10011 When DIFF=0, AD20 is selected as input; when DIFF=1, it is reserved.</li> <li>10100 When DIFF=0, AD21 is selected as input; when DIFF=1, it is reserved.</li> <li>10101 When DIFF=0, AD21 is selected as input; when DIFF=1, it is reserved.</li> <li>10111 When DIFF=0, AD22 is selected as input; when DIFF=1, it is reserved.</li> <li>10111 When DIFF=0, AD23 is selected as input; when DIFF=1, it is reserved.</li> <li>10111 When DIFF=0, AD23 is selected as input; when DIFF=1, it is reserved.</li> <li>11000 Reserved.</li> <li>11001 Reserved.</li> <li>11001 Reserved.</li> <li>11010 When DIFF=0, Temp Sensor (single-ended) is selected as input; when DIFF=1, Temp Sensor (differential) is selected as input.</li> <li>11011 When DIFF=0, Bandgap (single-ended) is selected as input; when DIFF=1, Bandgap (differential) is selected as input.</li> </ul>                   |

|       | <ul> <li>01101 When DIFF=0, AD13 is selected as input; when DIFF=1, it is reserved.</li> <li>01110 When DIFF=0, AD14 is selected as input; when DIFF=1, it is reserved.</li> <li>01111 When DIFF=0, AD15 is selected as input; when DIFF=1, it is reserved.</li> <li>10000 When DIFF=0, AD16 is selected as input; when DIFF=1, it is reserved.</li> <li>10010 When DIFF=0, AD17 is selected as input; when DIFF=1, it is reserved.</li> <li>10010 When DIFF=0, AD18 is selected as input; when DIFF=1, it is reserved.</li> <li>10011 When DIFF=0, AD19 is selected as input; when DIFF=1, it is reserved.</li> <li>10101 When DIFF=0, AD20 is selected as input; when DIFF=1, it is reserved.</li> <li>10100 When DIFF=0, AD21 is selected as input; when DIFF=1, it is reserved.</li> <li>10101 When DIFF=0, AD21 is selected as input; when DIFF=1, it is reserved.</li> <li>10110 When DIFF=0, AD22 is selected as input; when DIFF=1, it is reserved.</li> <li>10111 When DIFF=0, AD23 is selected as input; when DIFF=1, it is reserved.</li> <li>10111 When DIFF=0, Temp Sensor (single-ended) is selected as input; when DIFF=1, Temp Sensor (differential) is selected as input.</li> <li>11011 When DIFF=0,Bandgap (single-ended) is selected as input; when DIFF=1, Bandgap (differential is selected as input.</li> <li>11100 Reserved.</li> <li>11101 Reserved.</li> <li>11101 When DIFF=0,V<sub>REFSH</sub> is selected as input; when DIFF=1, -V<sub>REFSH</sub> (differential) is selected as</li> </ul> |