# **Engr354: Digital Logic Circuits**

**Chapter 4: Logic Optimization**

**Curtis Nelson**

## **Logic Optimization**

In chapter 4 you will learn about

- Synthesis of logic functions;

- Analysis of logic circuits;

- Techniques for deriving minimum-cost implementations;

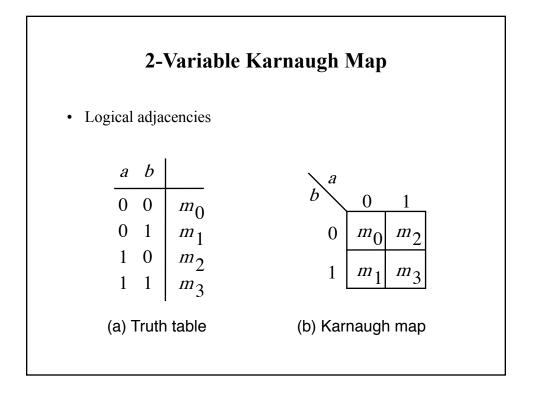

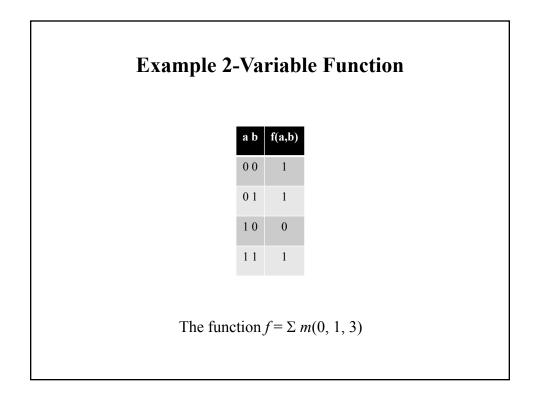

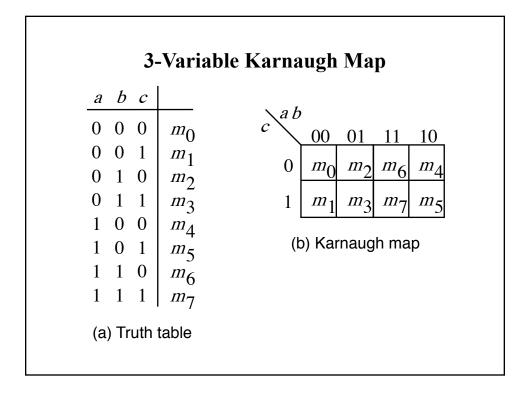

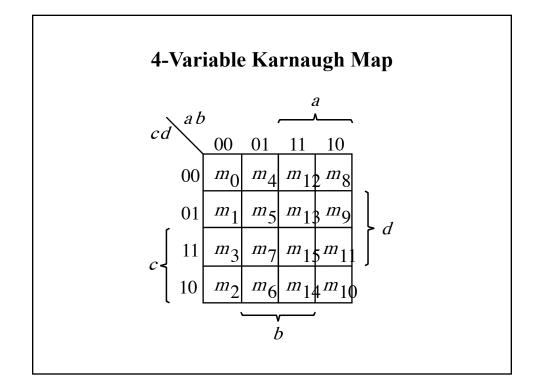

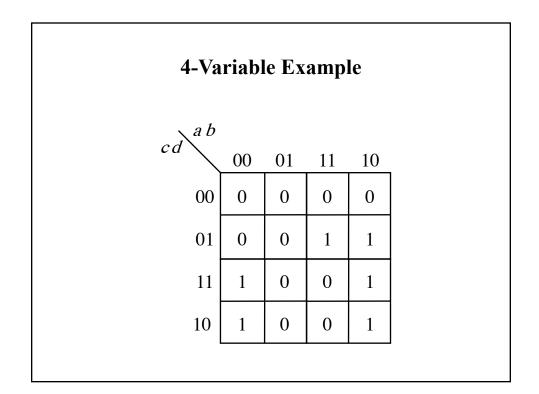

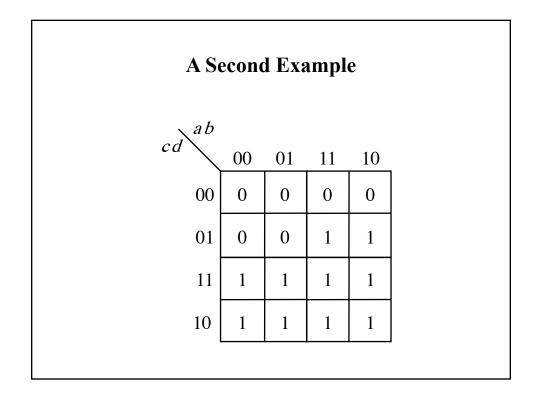

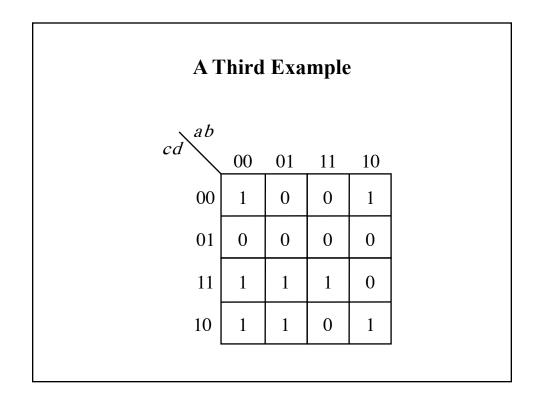

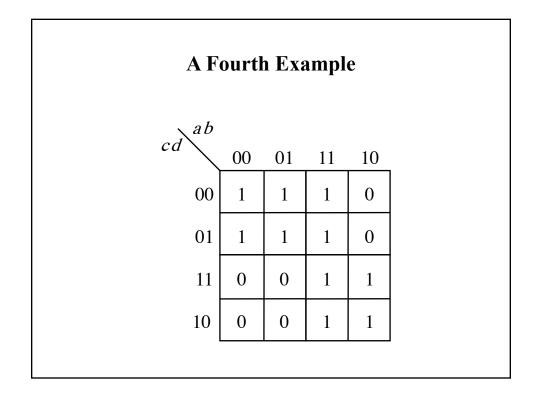

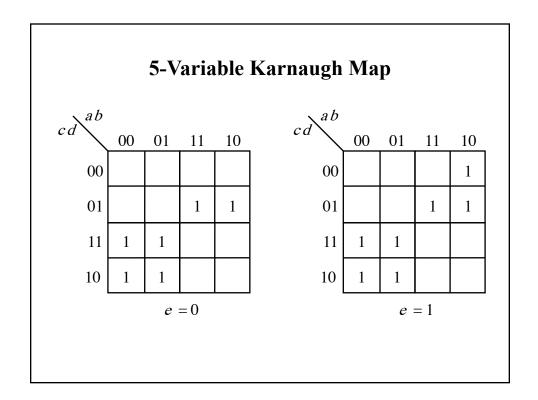

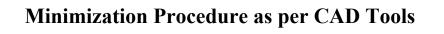

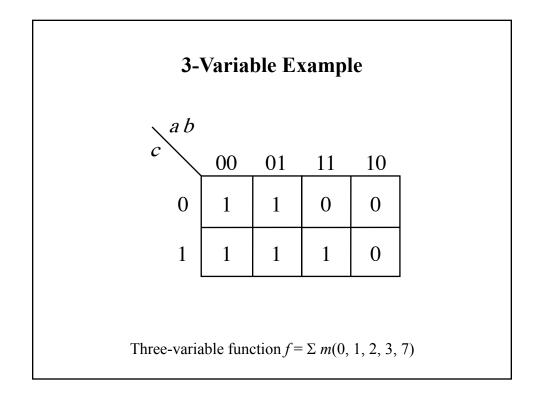

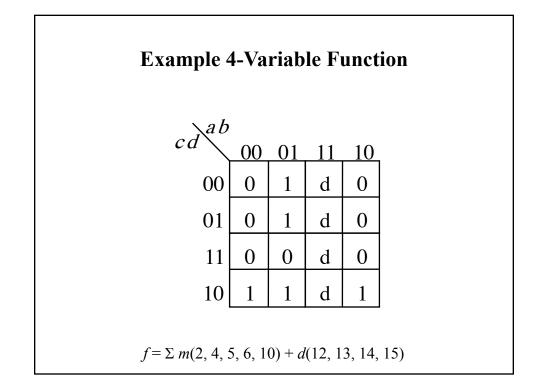

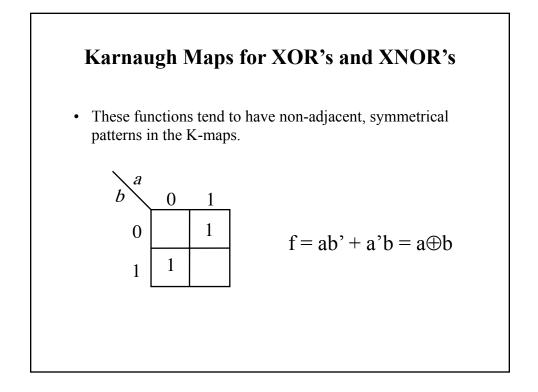

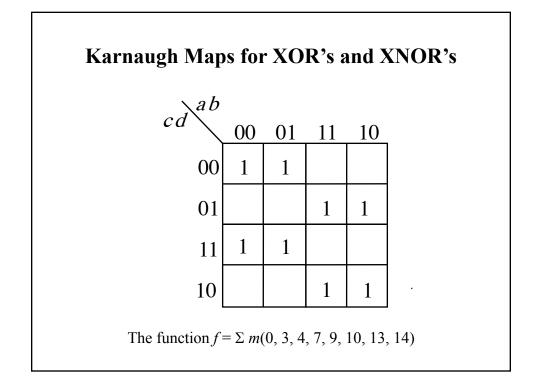

- Graphical representation of logic functions (Karnaugh maps);

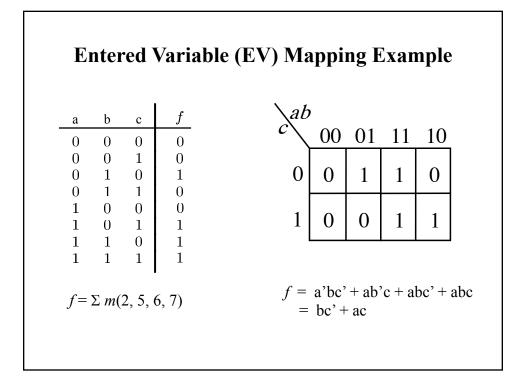

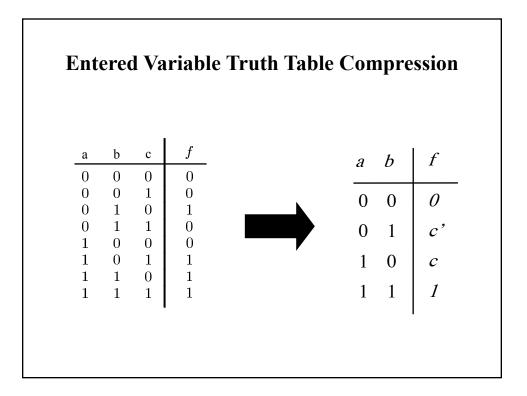

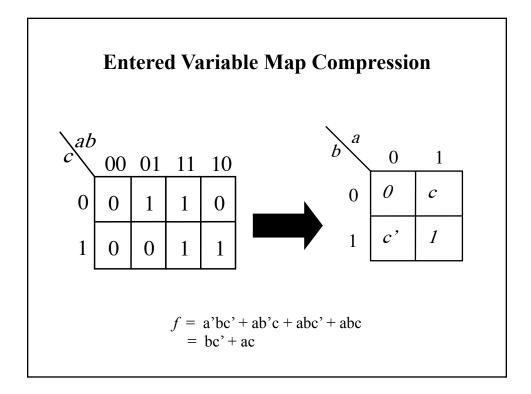

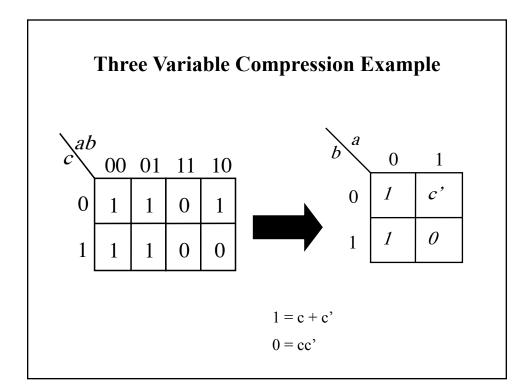

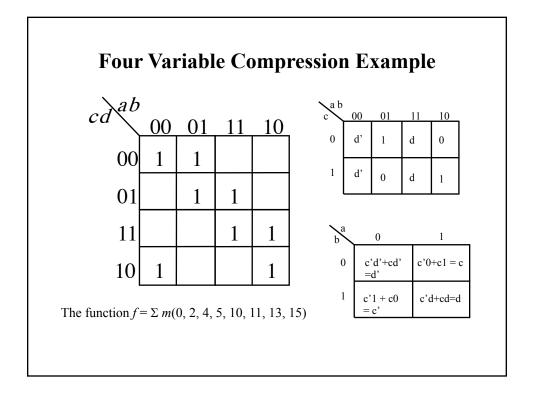

- Entered-variable mapping;

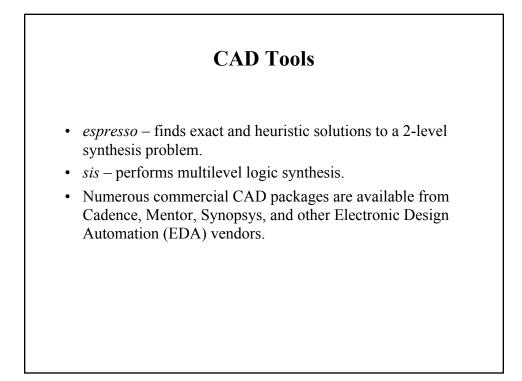

- Use of CAD tools to implement logic functions.

#### Motivation

- It is difficult to minimize a function using algebraic manipulation alone because it is not systematic;

- Graphical techniques allow for a more systematic (and visual) approach to minimization;

- Although software tools are used for logic optimization, designers like us must understand the process;

- This chapter presents methods for logic minimization that can be automated using CAD tools.

| • Minimizing with | <b>Example</b>        |        |       |       |  |

|-------------------|-----------------------|--------|-------|-------|--|

| Winninzing with   | algebra call          | oc um  | licun | •     |  |

|                   | Row Number            | a b c  | f     |       |  |

|                   | 0                     | 000    | 1     |       |  |

|                   | 1                     | 001    | 0     |       |  |

|                   | 2                     | 010    | 1     |       |  |

|                   | 3                     | 011    | 0     |       |  |

|                   | 4                     | 100    | 1     |       |  |

|                   | 5                     | 101    | 1     |       |  |

|                   | 6                     | 110    | 1     |       |  |

|                   | 7                     | 111    | 0     |       |  |

| The f             | $function f = \Sigma$ | E m(0, | 2, 4, | 5, 6) |  |

| $\begin{array}{c cccc} 0 & 0 & 0 & 0 & 1 \\ \hline 1 & 0 & 0 & 1 \\ \hline 1 & 0 & 0 & 1 \\ \hline 2 & 0 & 1 & 0 \\ \hline 2 & 0 & 1 & 0 \\ \hline 3 & 0 & 1 & 1 \\ \hline 4 & 1 & 0 & 1 \\ \hline 5 & 1 & 0 & 1 \\ \hline 6 & 1 & 1 & 0 \\ \hline 7 & 1 & 1 & 1 \end{array}$ | Ĩ | ole 3-Va | a b c |   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------|-------|---|

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                         |   |          |       |   |

| $\begin{array}{c ccccc} 3 & 0 & 1 & 1 & 0 \\ 4 & 1 & 0 & 0 & 1 \\ 5 & 1 & 0 & 1 & 1 \\ 6 & 1 & 1 & 0 & 1 \end{array}$                                                                                                                                                         |   | 1        |       | 0 |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                         |   | 2        | 010   | 1 |

| 5         1 0 1         1           6         1 1 0         1                                                                                                                                                                                                                 |   | 3        | 011   | 0 |

| 6 110 1                                                                                                                                                                                                                                                                       |   | 4        | 100   | 1 |

|                                                                                                                                                                                                                                                                               |   | 5        | 101   | 1 |

| 7 111 0                                                                                                                                                                                                                                                                       |   | 6        | 110   | 1 |

|                                                                                                                                                                                                                                                                               |   | 7        | 111   | 0 |

## Terminology

- A variable either uncomplemented or complemented is called a *literal;*

- A product term that indicates when a function is equal to 1 is called an *implicant;*

- An implicant that cannot be combined into another implicant that has fewer literals is called a *prime implicant;*

- A *cover* is a collection of implicants that accounts for all input combinations in which a function evaluates to 1;

- An *essential prime implicant* includes a minterm covered by no other prime;

- *Cost* is the number of gates plus the number of gate inputs, assuming primary inputs are available in both true and complemented form.

- Generate all prime implicants;

- Find all essential prime implicants;

- If essential primes do not form a cover, then select a minimal set of non-essential primes.

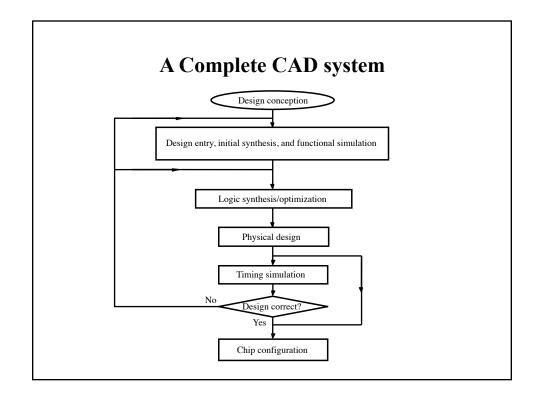

## **Physical Design**

- *Physical design* determines how logic is to be implemented in the target technology

- *Placement* determines where in the target device a logic function is realized;

- *Routing* determines how devices are to be interconnected using wires.

#### Summary

In this chapter you learned about:

- Synthesis of logic functions;

- Analysis of logic circuits;

- Techniques for deriving minimum-cost implementations;

- Graphical representation of logic functions (Karnaugh maps);

- Entered variable mapping;

- Use of CAD tools to implement logic functions.