# **Engr354: Digital Logic Circuits**

## **Chapters 8** Sequential Logic Design Principles

Dr. Curtis Nelson

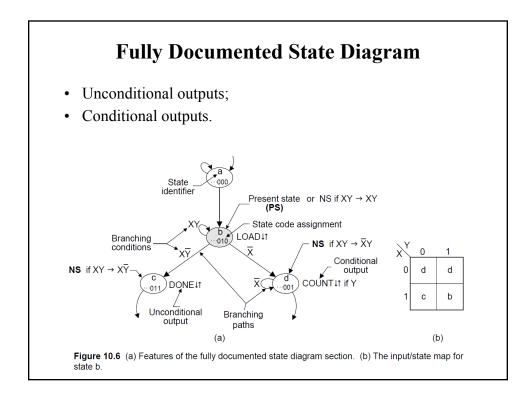

#### **Sequential Logic Design Principles**

In this chapter you will learn about:

- Design techniques for circuits that use flip-flops;

- State diagrams;

- Clocked synchronous state-machines;

- Clocked synchronous state-machine design.

## **Circuit Type Review**

- *Combinational* output depends only on the input;

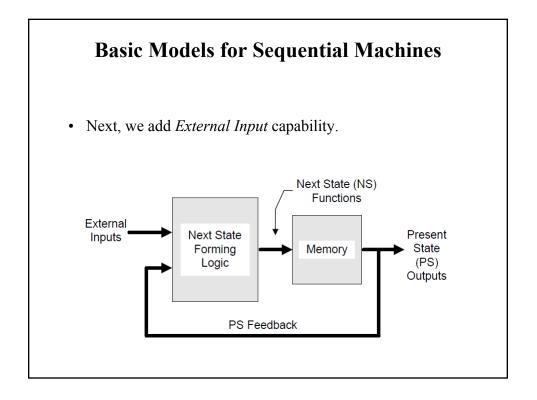

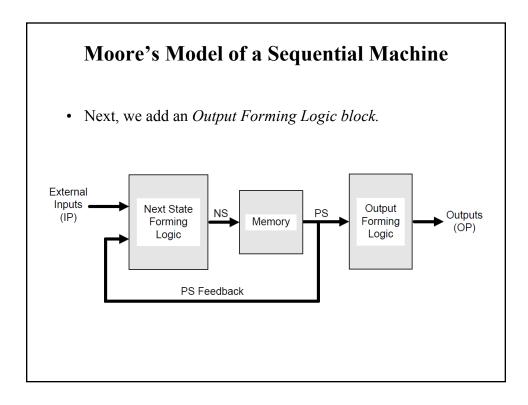

- Sequential output depends on input and past behavior:

- Requires use of storage elements;

- Contents of the storage elements are called *state;*

- Circuit goes through a sequence of states as a result of changes in inputs.

- *Synchronous* controlled by a clock.

# Summary of Terminology

- Basic cell cross-coupled NAND/NOR.

- Gated latch output may change only when *Clk* asserted:

- Gated SR latch;

- Gated D latch;

- Gated JK latch.

- Flip-flop output may change only on *Clk* edge:

- Master-slave;

- Edge-triggered;

- Three main types;

- D (very, very common, 74HC74);

- JK (hardly ever used, 74HC109);

- Toggle (occasionally used by CAD programs).

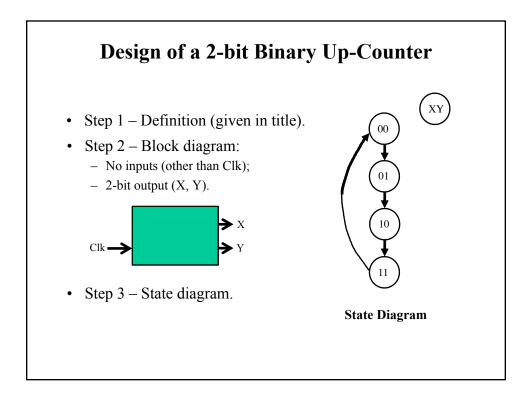

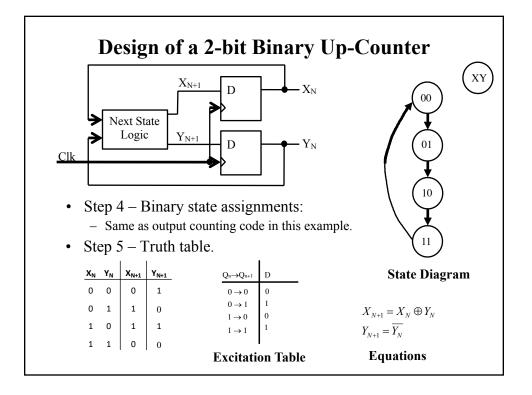

#### **State Machine Design Process**

- 1. Get design specifications;

- 2. Create a block diagram specifying all inputs and outputs;

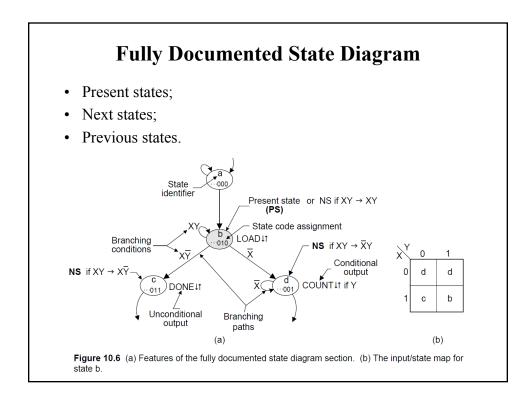

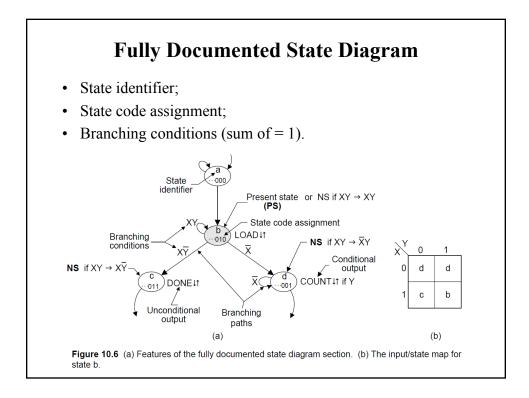

- 3. Design a state diagram using as few states as possible;

- 4. Make binary state assignments, maximizing logical adjacencies in the K-maps;

- 5. Plot entered variable K-maps;

- 6. Read minimum next state decoder logic;

- 7. Develop output decoder logic by plotting the output K-maps;

- 8. Draw schematic;

- 9. Do a logic simulation before wiring your circuit.

## **Sequential Logic Design Principles Summary**

In this chapter you learned about:

- Design techniques for circuits that use flip-flops;

- State diagrams;

- Clocked synchronous state-machines;

- Clocked synchronous state-machine design.