# **Chapter 1** Digital System Design

# Dr. Curt Nelson Engr433 – Digital Design

# Outline

- 1. Why Digital?

- 2. Device Technologies

- 3. System Representation

- 4. Abstraction

- 5. Development Tasks

- 6. Development Flow

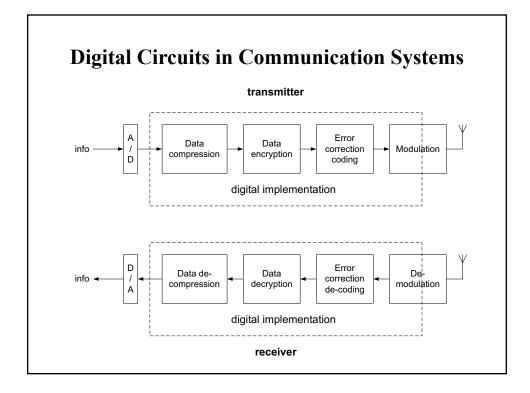

# Why Digital? Advantages of digital devices Reproducibility of information; Flexibility and functionality - easier to store, transmit and manipulate information; Economy - cheaper devices and easier to design. Moore's law Transistor geometry; Chips double in density (number of transistor) every 18 months; Devices become smaller, faster, and cheaper; Now, a chip consists of a few billion gates.

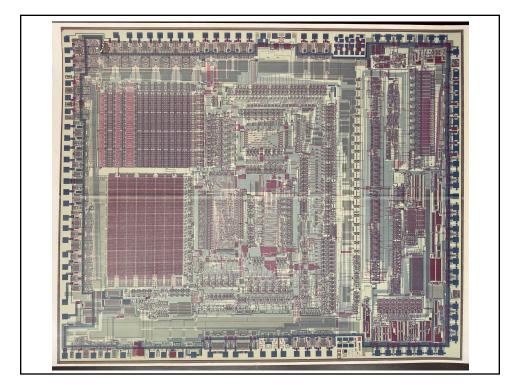

# **Device Technologies - Fabrication of an IC**

- Transistors and connections are made from many layers (typically 10 to 15 in CMOS) built on top of one another;

- Each layer has a special pattern defined by a mask;

- One important aspect of an IC is the length of a smallest transistor that can be fabricated

- Measured in microns (10<sup>-6</sup> meter);

- We may say an IC is built with 15 nm process;

- The process continues to improve, as witnessed by Moore's law;

- The state-of-art processes are now 9 nm and shrinking, still using photolithography.

- In a fabrication facility ASIC (Application Specific IC);

- In the "field" non-ASIC, like an FPGA.

- Classification

- Full-custom ASIC;

- Standard cell ASIC;

- Gate array ASIC;

- Field programmable logic device;

- Off-the-shelf parts (Small or Medium Scale Integration).

# **Full-Custom ASIC**

- All aspects (e.g., size of a transistor) of a circuit are tailored for a particular application;

- Circuit fully optimized;

- Design extremely complex and involved;

- Masks needed for all layers.

#### **Standard-Cell ASIC**

- Circuit made of a set of pre-defined logic, known as standard cells, e.g. basic logic gates like 1-bit adder, D FF, NAND gates, etc.

- Layout of a cell is pre-determined, but layout of the complete circuit is customized;

- Masks needed for all layers.

# **Gate-Array ASIC**

- Circuit is built from an array of a single type of cell (known as base cell);

- Base cells are pre-arranged and placed in fixed positions, aligned as one- or two-dimensional arrays;

- More sophisticated components (macro cells) can be constructed from base cells;

- Masks needed only for metal layers (connection wires).

# Field Programmable Device

- Device consists of an array of generic logic cells and general interconnect structure;

- Logic cells and interconnect can be "programmed" by utilizing semiconductor fuses or switches;

- Customization is done in the field;

- No custom masks needed.

#### **SSI/MSI** Components

- Small parts with fixed, limited functionality;

- e.g. 74HC00 CMOS series (more than 100 parts);

- Resource (e.g., power, board area, manufacturing cost etc.) is consumed by *package* but not *silicon*;

- Seldom a viable option.

# **Three Viable Technologies**

- Standard Cell ASIC;

- Gate Array ASIC;

- FPGA.

| <i>«</i> ۳     | FPGA            | Gate array | Standard cell  |

|----------------|-----------------|------------|----------------|

| tailored masks | 0               | 3 to 5     | 15 or more     |

| area           |                 |            | best (smallest |

| speed          |                 |            | best (fastest) |

| power          |                 |            | best (minimal  |

| NRE cost       | best (smallest) |            |                |

| per part cost  |                 |            | best (smallest |

| design cost    | best (easiest)  |            |                |

| time to market | best (shortest) |            |                |

| per unit cost  | depend on volum |            |                |

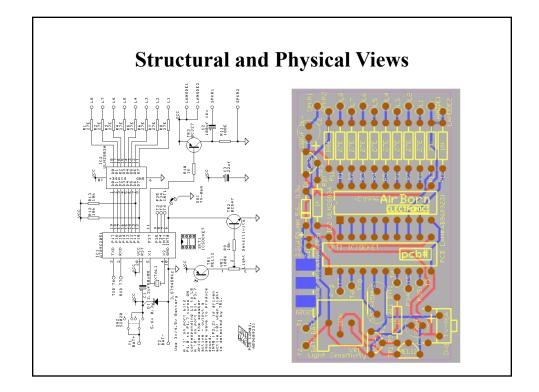

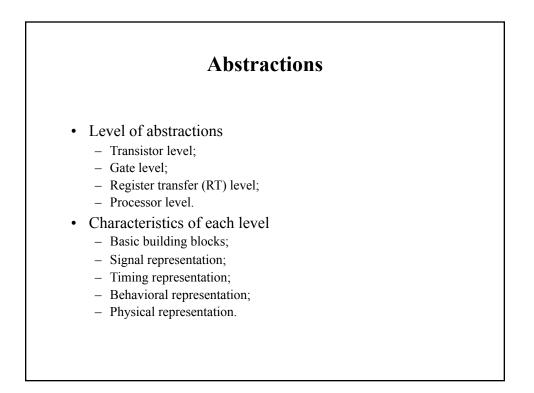

| Summary    |                            |                          |                        |                           |                         |  |  |

|------------|----------------------------|--------------------------|------------------------|---------------------------|-------------------------|--|--|

|            | typical<br>blocks          | signal<br>representation | time<br>representation | behavioral<br>description | physical<br>description |  |  |

| transistor | transistor,<br>resistor    | voltage                  | continuous<br>function | differential equation     | transistor<br>layout    |  |  |

| gate       | and, or, xor,<br>flip-flop | logic 0 or 1             | propagation<br>delay   | Boolean<br>equation       | cell<br>layout          |  |  |

| RT         | adder, mux,<br>register    | integer,<br>system state | clock tick             | extended<br>FSM           | RT level<br>floor plan  |  |  |

| processor  | processor,<br>memory       | abstract<br>data type    | event<br>sequence      | algorithm<br>in C         | IP level<br>floor plan  |  |  |

# **Methods of Verification**

- Simulation

- Spot check: cannot verify the absence of errors;

- Can be computationally intensive.

- Timing analysis

- Just check delay.

- · Formal verification

- Apply formal math techniques to determine properties;

- E.g, equivalence checking.

- Hardware emulation

### Testing

- Testing is the process of detecting physical defects of a die or a package occurring at the time of manufacturing;

- Testing and verification are different tasks;

- Difficult for large circuits

- Need to add auxiliary testing circuits into the design;

- E.g., built-in self test (BIST), scan chain etc.

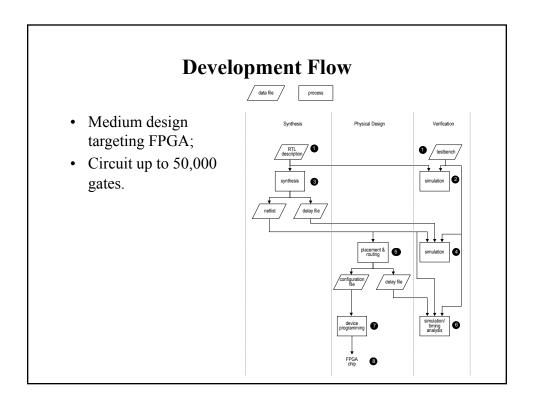

### **Additional Tasks**

- Large design targeting FPGA

- Design partitioning;

- More verification.

- Large design targeting ASIC

- Thorough verification;

- Testing;

- Physical design.