# Chapter 4 Concurrent Signal Assignment Statements

Dr. Curt Nelson Engr433 – Digital Design

# Outline

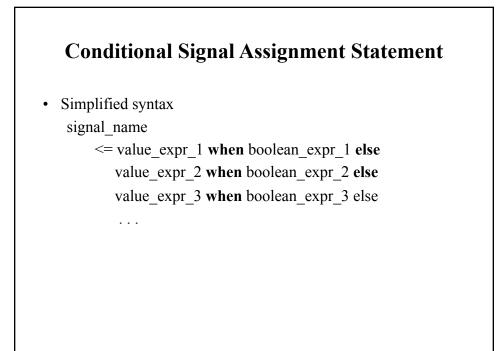

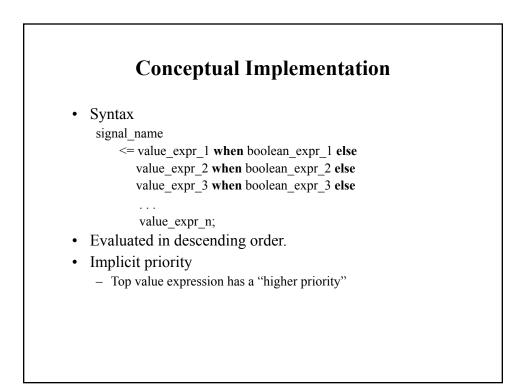

Combinational versus sequential circuits; Simple signal assignment statement; Conditional signal assignment statement; Selected signal assignment statement; Conditional vs. selected signal assignment.

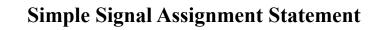

- Simple signal assignment is a special case of conditional signal assignment.

- Syntax

signal\_name <= value\_expression;</pre>

• Example

```

y <= a + b + 1 after 10 ns;

```

• Timing info is ignored in synthesis and  $\delta$ -delay (tiny delay) is used instead.

| Example: 4-to-1 Mux                                                                                                                                                                 |                                     |                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|------------------|

| library ieee;<br>use ieee.std_logic_1164.all;<br>entity mux4 is<br>port(<br>a,b,c,d: in std_logic_vector(7                                                                          | downto 0                            | ):               |

| -                                                                                                                                                                                   |                                     | , ,              |

| s: in std_logic_vector(1 downt                                                                                                                                                      | o 0);                               | ,                |

| -                                                                                                                                                                                   | o 0);                               | . ,              |

| s: in std_logic_vector(1 downt<br>x: out std_logic_vector(7 down                                                                                                                    | o 0);                               |                  |

| <pre>s: in std_logic_vector(1 downt     x: out std_logic_vector(7 down ); end mux4 ; architecture cond_arch of mux4 is</pre>                                                        | o 0);<br>ito 0)                     |                  |

| <pre>s: in std_logic_vector(1 downt     x: out std_logic_vector(7 down );</pre>                                                                                                     | o 0);                               |                  |

| <pre>s: in std_logic_vector(1 downt</pre>                                                                                                                                           | o 0);<br>ito 0)<br>input            | output           |

| <pre>s: in std_logic_vector(1 downt<br/>x: out std_logic_vector(7 down<br/>);<br/>end mux4 ;<br/>architecture cond_arch of mux4 is<br/>begin<br/>x &lt;= a when (s="00") else</pre> | o 0);<br>(to 0)<br>input<br>s       | output<br>x      |

| <pre>s: in std_logic_vector(1 downt</pre>                                                                                                                                           | o 0);<br>(to 0)<br>input<br>s<br>00 | output<br>x<br>a |

# **Example: 2-to-2<sup>2</sup> Binary Decoder**

```

library ieee;

use ieee.std_logic_1164.all;

entity decoder4 is

port (

s: in std_logic_vector(1 downto 0);

x: out std_logic_vector(3 downto 0)

);

end decoder4 ;

architecture cond_arch of decoder4 is

input

output

begin

s

x \le "0001" when (s="00") else

х

"0010" when (s="01") else

0.0

0001

"0100" when (s="10") else

01

0010

"1000";

1 \ 0

0100

end cond_arch;

1 \ 1

1000

```

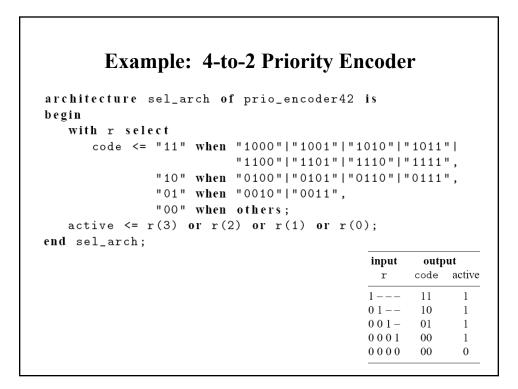

| <b>Example: 4-to-2 Priority Encoder</b>                                                     |       |          |       |  |

|---------------------------------------------------------------------------------------------|-------|----------|-------|--|

| library ieee;                                                                               |       |          |       |  |

| use ieee.std_logic_1164.all;                                                                |       |          |       |  |

| entity prio_encoder42 is                                                                    |       |          |       |  |

| port (                                                                                      |       |          |       |  |

| <pre>r: in std_logic_vector(3 downto 0);</pre>                                              |       |          |       |  |

| code: <b>out</b> std_logic_vector(1 <b>downto</b> 0)                                        | ;     |          |       |  |

| active: <b>out</b> std_logic                                                                |       |          |       |  |

| );                                                                                          |       |          |       |  |

| end prio_encoder42;                                                                         |       |          |       |  |

| architecture cond_arch of prio_encoder42 is                                                 | input | outp     | ut    |  |

| h t                                                                                         | r     | code     | activ |  |

| begin<br>code <= "11" when (r(3)='1') else                                                  |       |          | 1     |  |

| code <= "11" when (r(3)='1') else                                                           | 1     | 11       | 1     |  |

| 5                                                                                           | 1     |          | -     |  |

| code <= "11" when (r(3)='1') else<br>"10" when (r(2)='1') else                              | 01    | 10       | 1     |  |

| code <= "11" when (r(3)='1') else<br>"10" when (r(2)='1') else<br>"01" when (r(1)='1') else | -     | 10<br>01 | -     |  |

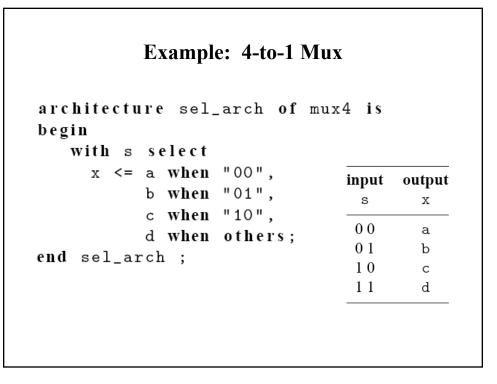

### **Example: 2-to-2<sup>2</sup> Binary Decoder**

```

architecture sel_arch of decoder4 is

begin

with sel select

x \le "0001" when "00",

"0010" when "01",

input

output

"0100" when "10",

х

S

"1000" when others;

0.0

0001

end sel_arch ;

01

0010

1.0

0100

11

1000

```

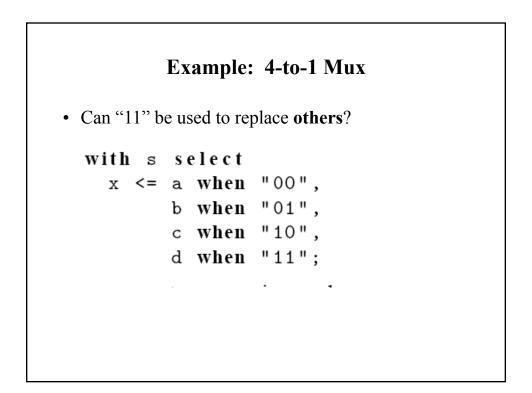

# Example: 4-to-1 Mux • Can we use '-'? with a select x <= "11" when "1---", "10" when "01--", "01" when "001-", "00" when others; • Note implied priority.

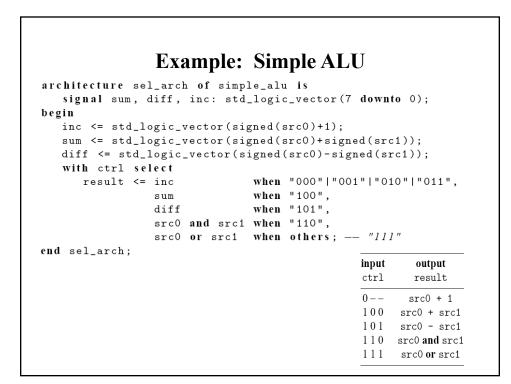

| library ieee;<br>use ieee.std_logic_1164.all; | input | - |

|-----------------------------------------------|-------|---|

| entity truth_table is                         | ab    | У |

| port (                                        | 0.0   | 0 |

| a, b: in std_logic;                           | 01    | 1 |

| y: out std_logic<br>);                        | 10    | 1 |

| end truth_table;                              | 11    | 1 |

| architecture a of truth_table is              |       |   |

| signal tmp: std_logic_vector(1 downto         | 0);   |   |

| begin                                         |       |   |

| tmp <= a & b;                                 |       |   |

| with tmp select                               |       |   |

| y <= '0' when "00",                           |       |   |

| '1' when "01",                                |       |   |

| '1' when "10",                                |       |   |

| '1' when others; "11"                         |       |   |

```

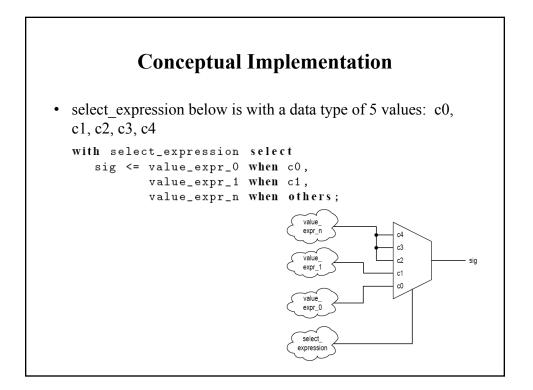

sig <=

value_expr_0 when c0,

value_expr_1 when c1|c3|c5,

value_expr_2 when c2|c4,

value_expr_n when others;

sig <=

value_expr_1 when (sel=c0) else

value_expr_1 when (sel=c1) or (sel=c3) or (sel=c5) else

value_expr_2 when (sel=c2) or (sel=c4)else

value_expr_n;</pre>

```

```

From Conditional Assignment to Selected Assignment

sig <= value_expr_0 when bool_exp_0 else

value_expr_1 when bool_exp_1 else

value_expr_2 when bool_exp_2 else

value_expr_n;

sel(2) <= '1' when bool_exp_0 else '0';

sel(0) <= '1' when bool_exp_2 else '0';

sel(0) <= '1' when bool_exp_2 else '0';

with sel select

sig <= value_expr_0 when "100"|"101"|"110"|"111",

value_expr_1 when "010"|"011",

value_expr_2 when "001",

value_expr_n when others;</pre>

```

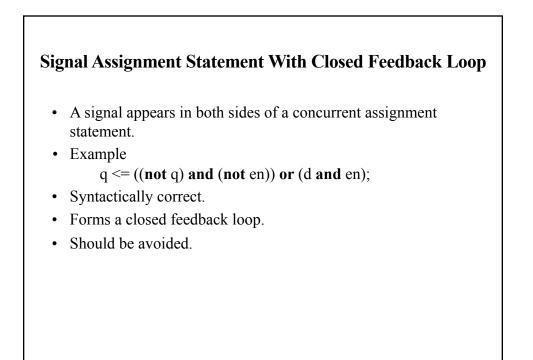

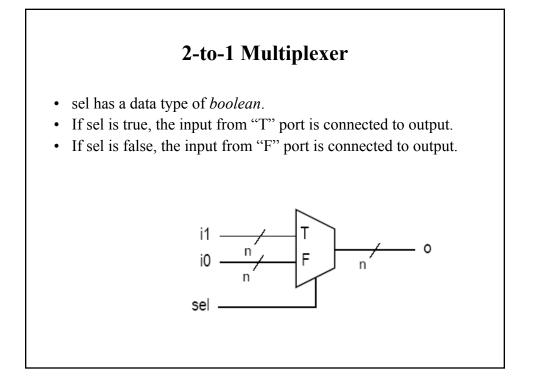

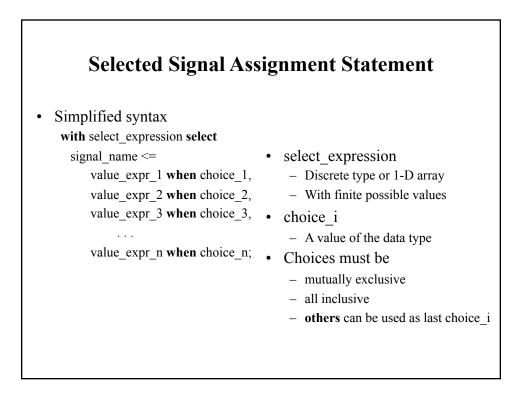

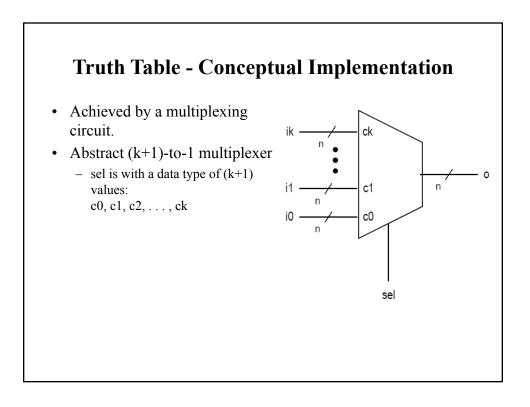

## Comparison

- Selected signal assignment

- Good match for a circuit described by a functional table;

- E.g., binary decoder, multiplexer;

- Less effective when an input pattern is given a preferential treatment.

- Conditional signal assignment:

- Good match for a circuit that needs to give preferential treatment for certain conditions or to prioritize the operations;

- E.g., priority encoder;

- Can handle complicated conditions like this

```

pc_next <=

pc_reg + offset when (state=jump and a=b) else

pc_reg + 1 when (state=skip and flag='1') else

. . .</pre>

```